- 1:0x00 综述

- 2:0x01 AHB总线信号

- 3:0x02 AHB互联方式

- 3.1:单主设备的互联方式

- 3.2:多主设备的互联方式

- 4:0x03 AHB传输时序

- 5:0x04 参考文献

0x00 综述

AHB总线拥有多个版本:

- AMBA 2 AHB - 是AHB的第一个发行版,该版本使用了一对握手信号(总线请求和总线授权)用于多个主设备之间的请求仲裁。

- 多层AHB设计 - ARMAMBA设计套件产品中包含了名为AHB总线矩阵的AHB互联组件。这允许多个主设备的系统在共同传输时拥有更高的带宽,并去除了总线请求和总线授权信号,该版本被非官方地称为“AHB Lite”。

- AHB Lite在AMBA 3规范中变为了官方名称。该版本移除了总线请求和总线授权信号,并简化了AHB协议的其它部分。该版本被广泛应用于大量ARM处理器系统中。

- 在AMBA 5规范中,AHBJ加入了可信区功能支持,该功能面向Armv8-M系列处理器,并加入了对排他访问边缘信号的官方支持。同时也引入了额外的一些Cache属性支持,并进行了相应简化。

目前AMBA 5 AHB(或者叫做AHB5)是AHB规范的最新发行版,该版本具有高度的向下兼容性,为AHB Lite设计的已存在的从设备也可以重用于AHB5系统中。

0x01 AHB总线信号

通常情况下,AHB总线拥有如下信号:

| 信号 | 方向 | 描述 |

|---|---|---|

| HCLK | 时钟源->全部AHB块 | 公共时钟信号 |

| HRESETn | 复位源->全部AHB块 | 公共低有效复位信号 |

| HSEL | 地址译码器->从设备 | 设备选择 |

| HADDR[31:0] | 主设备->从设备 | 地址总线 |

| HTRANS[1:0] | 主设备->从设备 | 传输控制 |

| HWRITE | 主设备->从设备 | 写控制(1=写,0=读) |

| HSIZE[2:0] | 主设备->从设备 | 传输大小控制 |

| HBURST[2:0] | 主设备->从设备 | 传输突发类型控制 |

| HPROT[3:0]/[6:0] | 主设备->从设备 | 传输保护控制,在AHB Lite中为4bit,在AHB5中为7bit |

| HMASTLOCK | 主设备->从设备 | 传输加锁控制,表明传输是序列原子的 |

| HMASTER[3:0] | 总线组件->从设备 | 表示当前总线的主设备标识符,即表示当前传输的主设备,但在一些Cortex-M处理器中,该信号用于表示传输类型(例如表示传输是否来自调试器,该信号的位宽可以根据具体的系统需求定制) |

| HWDATA[31:0] | 主设备->从设备 | 写出的数据(通常为32bit,但在64bit系统中为64bit) |

| HRDATA[31:0] | 从设备->主设备 | 读入的数据(通常为32bit,但在64bit系统中为64bit) |

| HRESP[1:0] / HRESP | 从设备->主设备 | 从设备响应(在AMBA 2中为2bit,在AHB Lite以及AHB5中为1bit) |

| HREADY (HREADYOUT) | 从设备->主设备(HREADYOUT),总线组件->其它从设备(HREADY) | 从设备已准备好(传输完成)。HREADY信号有两个方向,当前选中的从设备向主设备或者是其它的AHB从设备驱动HREADY,因此一个AHB从设备拥有方向为输入的HREADY信号以及方向为输出的HREADYOUT信号 |

AMBA 5 AHB引入了额外的信号:

| 信号 | 方向 | 描述 |

|---|---|---|

| HNONSEC | 主设备->从设备 | 用于传输的安全属性(需要可信区安全扩展) |

| HEXCL | 主设备->从设备 | 表示传输是排他访问的 |

| HEXOKAY | 从设备->主设备 | 排他访问成功响应 |

| HAUSER | 主设备->从设备 | 地址阶段信号的可选用户边缘信号(该信号实际由具体的系统自行定义,一般情况下会用来表示本次传输的其它额外信息以及地址阶段的控制信号奇偶校验位等) |

| HWUSER | 主设备->从设备 | 数据阶段信号的可选用户边缘信号(该信号实际由具体的系统自行定义,一般情况下用于写出数据的奇偶校验位) |

| HRUSER | 从设备->主设备 | 数据阶段信号的可选用户边缘信号(该信号实际由具体的系统自行定义,一般情况下爱用于读入数据的奇偶校验位) |

在更早的AHB系统(AMBA 2)中使用AHB仲裁器来处理多主设备访问,该功能使用了以下信号:

| 信号 | 方向 | 描述 |

|---|---|---|

| HBUSREQ | 主设备->仲裁器 | 总线访问请求 |

| HGRANT | 仲裁器->主设备 | 总线已授权 |

| HLOCK | 主设备->仲裁器 | 加锁传输控制 |

| HMASTLOCK | 从设备->仲裁器 | 传输加锁控制。更新的AHB系统没有使用仲裁器,HMASTLOCK信号由主设备或者总线互联器生成 |

上述的很多信号都是可选的,在一个单Arm Cortex-M0处理器中,实现一个最小的AHB系统只需要以下几个信号:HCLK、HRESETn、HADDR、HTRANS、HSIZE、HWRITE、HSEL、HWDATA、HRDATA、HRESP、HREADY。

HTRANS信号表示传输类型,大多数的AHB系统并不需要在全部的时间处理数据传输,当一个主设备不需要立即开启另一个传输时,它就可以发送一个空闲传输,HTRANS信号用于表示当前传输为活动传输还是空闲传输,具体取值含义如下:

| HTRANS[1:0] | 描述 |

|---|---|

| 00 | Idle 空闲(非活动) |

| 01 | Busy 忙(非活动) |

| 10 | Non-Sequential 非顺序的(活动) |

| 11 | Sequential 顺序的(活动) |

其中,非顺序传输通常用于一般的传输及一个突发传输的开始,而顺序传输则用于突发传输的剩余部分,表明本次传输是前序传输的接续。

空闲传输和忙传输表示总线上无实际的数据传输,其中忙传输仅在主设备开始了突发传输但又未准备好下次数据传输时使用。

通常情况下,HSIZE是一个3bit信号,但是大多数AHB系统只会使用该信号的低2bit,因此在一些系统中,该信号只有2bit,具体取值含义如下:

| HSIZE[2:0] | 传输大小 |

|---|---|

| 000 | 字节(8bit) |

| 001 | 半字(16bit) |

| 010 | 字(32bit) |

| 011 | 双字(64bit) |

| 100 | 128bit |

| 101 | 256bit |

| 110 | 512bit |

| 111 | 1024bit |

由于AHB不支持非对齐传输,因此主设备在传输时,必须保证传输的数据是对齐的。

在AMBA 2 AHB以及AHB Lite中,HPROT信号为4bit,定义如下:

| 信号 | 功能 | 值为0时 | 值为1时 |

|---|---|---|---|

| HPROT[0] | 数据/操作码 | 取指令 | 访问数据 |

| HPROT[1] | 特权级 | 非特权的(用户) | 特权的 |

| HPROT[2] | 可Buffer | 本次传输必须完成后才能启动一个新的传输 | 写传输可被Buffer |

| HPROT[3] | 可Cache | 数据不能被Cache | 数据可以被Cache |

当访问一般的存储器(非外设)时,HPROT[3:2]的编码可以取以下的值:

| HPROT[3:2] | 传输大小 |

|---|---|

| 00 | 设备(不可Buffer) |

| 01 | 设备(可Buffer) |

| 10 | 写穿模式的可Cache存储器 |

| 11 | 写回模式的可Cache存储器 |

在AMBA 5 AHB中,该属性被扩展,其定义如下所示:

| 信号 | 功能 | 值为0时 | 值为1时 |

|---|---|---|---|

| HPROT[0] | 数据/操作码 | 取指令 | 访问数据 |

| HPROT[1] | 特权级 | 非特权的(用户) | 特权的 |

| HPROT[2] | 可Buffer | 本次传输必须完成后才能启动一个新的传输 | 写传输可被Buffer |

| HPROT[3] | 可修改 | 数据不能被Cache | 数据可以被Cache |

| HPROT[4] | 查找 | 传输没有被Cache | 传输必须查找Cache |

| HPROT[5] | 分配 | 不需要进行Cache行分配 | 在Cache Miss时进行Cache行分配 |

| HPROT[6] | 可共享 | 数据没有被共享(不需要维护数据一致性)或者是向一个设备传输(不可Cache) | 总线互联器需要确保数据一致性 |

Cache类型如下表所示:

| HPROT[6] 可共享 | HPROT[5] 分配 | HPROT[4] 查找 | HPROT[3] 可修改 | HPROT[2] 可Buffer | 存储器类型 |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 不可Buffer设备 |

| 0 | 0 | 0 | 0 | 1 | 可Buffer设备 |

| 0 | 0 | 0 | 1 | 0 | 一般的不可Cache、不可共享存储器 |

| 0 | 0或1 | 1 | 1 | 0 | 写穿、不可共享存储器 |

| 0 | 0或1 | 1 | 1 | 1 | 写回、不可共享存储器 |

| 1 | 0 | 0 | 1 | 0 | 一般的不可Cache、可共享存储器 |

| 1 | 0或1 | 1 | 1 | 0 | 写穿、可共享存储器 |

| 1 | 0或1 | 1 | 1 | 1 | 写回、可共享存储器 |

HBURST信号用于在突发传输时表示突发类型,AHB支持以下几种突发类型:

- 单次传输(不是突发传输,每一次传输都是完全独立的)

- 递增突发传输(地址根据传输的大小递增)

- 回绕突发传输,对于每次传输,地址都会根据突发长度增加,但是一旦地址到达突发块大小边界,地址就会回绕到块大小边界的开始处,突发块大小由节拍数乘传输大小决定。

突发传输序列由多拍组成,每一拍都是一次AHB传输,其地址与突发传输中的其它传输相联系,在一次突发传输中,每次传输的传输大小、反向概念股及控制控制信息都必须相同,递增与回绕突发传输都支持4拍、8拍与16拍传输,增量突发传输也支持不指定拍数。

| HBURST[2:0] | 突发类型 | 描述 |

|---|---|---|

| 000 | Single | 单次传输(非突发) |

| 001 | INCR | 未指定拍数的递增突发传输 |

| 010 | WRAP4 | 4拍回绕传输 |

| 011 | INCR4 | 4拍递增传输 |

| 100 | WRAP8 | 8拍回绕传输 |

| 101 | INCR8 | 8拍递增传输 |

| 110 | WRAP16 | 16拍回绕传输 |

| 111 | INCR16 | 16拍递增传输 |

回绕传输在Cache控制器的设计中是比较有用的,相比于递增传输,这种传输方式可以首先传输处理器所需要的那个数据,然后,再传输同一Cache行中的其它数据,这就减少了处理器的等待时间。

这里有一点注意事项:突发传输不应该跨越多个AHB从设备,若一个突发传输在一个从设备上开始,又对另一个从设备进行操作,则另一个从设备接收到的第一个数据包传输类型是SEQ(即顺序的),这违反了AHB协议规定(即突发传输的第一次传输的传输类型必须为NSEQ(即非顺序的)。

HMASTLOCK信号用于锁定总线的所有者,以实现原子操作,当HMASTLOCK信号被使能时,总线机构将不允许切换总线所有者直到HMASTLOCK信号被释放。

HRESP信号用于表示AHB从设备的响应,在AMBA 2 AHB中,有四种取值,分别是OKAY、ERROR、RETRY、SPLIT,而在AHB LITE以及AHB5中,则仅有OKAY与ERROR两种取值。

AMBA 2 AHB的HRESP信号定义如下:

| HRESP[1:0] | 响应 | 描述 |

|---|---|---|

| 00 | OKAY | 传输成功完成 |

| 01 | ERROR | 传输发生了错误 |

| 10 | RETRY | AHB从设备不能立即完成传输,AHB主设备应当重试传输 |

| 11 | SPLIT | AHB从设备不能立即完成传输,AHB主设备可以释放总线所有权,当AHB从设备准备好时,主设备可以再次请求总线所有权以便完成传输 |

在传输类型为IDLE或BUSY时,或者从设备未被选中时,AHB从设备必须在HRESP上回应OKAY信号。

当AHB从设备反馈RETRY时,主设备必须通过将传输类型替换为IDLE的方式取消掉当前的传输,并立即重新启动最后一次失败的传输。

当AHB从设备反馈SPLIT时,主设备必须通过将传输类型替换为IDLE的方式取消掉当前传输并释放掉连接到仲裁器的HBUSREQ信号以便释放总线控制权,当AHB从设备准备好接收传输时,从设备会使用叫做HSPLIT的边缘信号让仲裁器恢复主设备的总线所有权,然后主设备就可以重启传输。

由于操作的复杂性,SPLIT响应与HSPLIT信号很少被使用,从2001年开始,多层AHB方法被发明出来,SPLIT和RETRY机制被废除,因为新的解决方案易用性更高,并且可以避免单词传输拖慢系统的其余部分,同时可以提升系统带宽。

有些Cortex-M处理器,例如Cortex-M3以及Cortex-M4拥有2bit宽的HRESP信号,但却为AHB Lite设计,这是因为这些处理器是在AHB Lite规范正式化之前发布的。当AHB Lite系统连接到这样的主设备时,可以将从设备的HRESP连接到主设备的HRESP[0],然后将HRESP[1]置为1来正确的连接。

HEXOKAY信号用于支持排他访问操作,该信号由总线系统的全局排他访问监视器产生。排他访问操作序列包括一个对相同数据的排他load操作与排他store操作。如果在load与store操作之间有其它的主设备修改了排他操作对应的数据,监视器就会阻止store操作并通过HEXOKAY返回排他失败状态。

当排他store发生时,如果全局排他访问监视器未检测到访问冲突,HEXOKAY会与HREADY在同一时钟周期一起被使能,否则,HEXOKAY会保留拉低状态(如果从设备不支持排他操作,可能会产生排他访问冲突错误)。

0x02 AHB互联方式

单主设备的互联方式

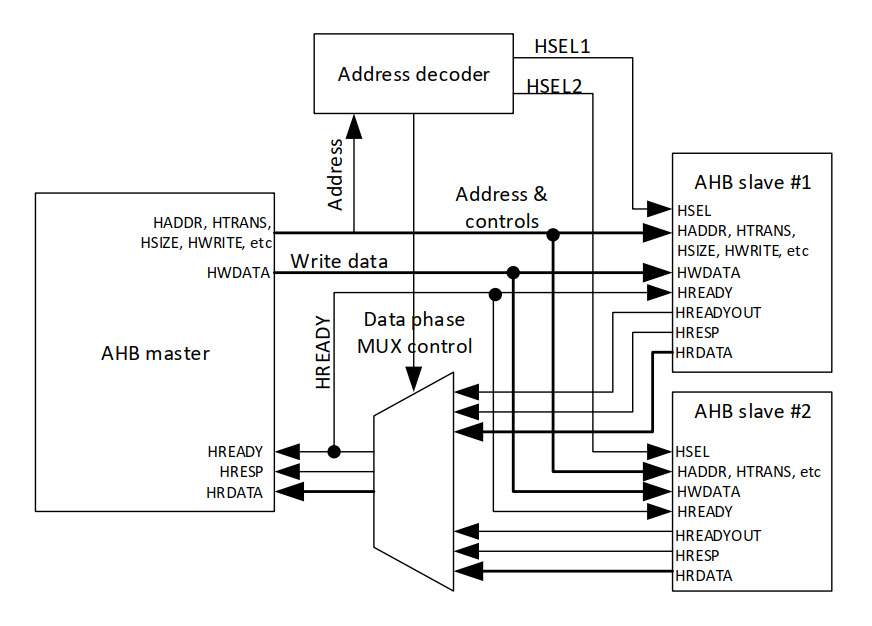

一个仅有一个主设备(例如,一个Cortex-M处理器)以及多个从设备的简单设计如下所示:

信号可以被分为地址阶段信号与数据阶段信号。

地址阶段信号如下所示:

- 必须:HADDR、HTRANS、HSEL、HWRITE、HSIZE

- 可选:HPROT、HBURST、HMASTLOCK、HEXCL、HAUSER

数据阶段信号如下所示:

- 必须:HWDATA、HRDATA、HRESP、HREADY(以及HREADYOUT)

- 可选:HEXOKAY、HWUSER、HRUSER

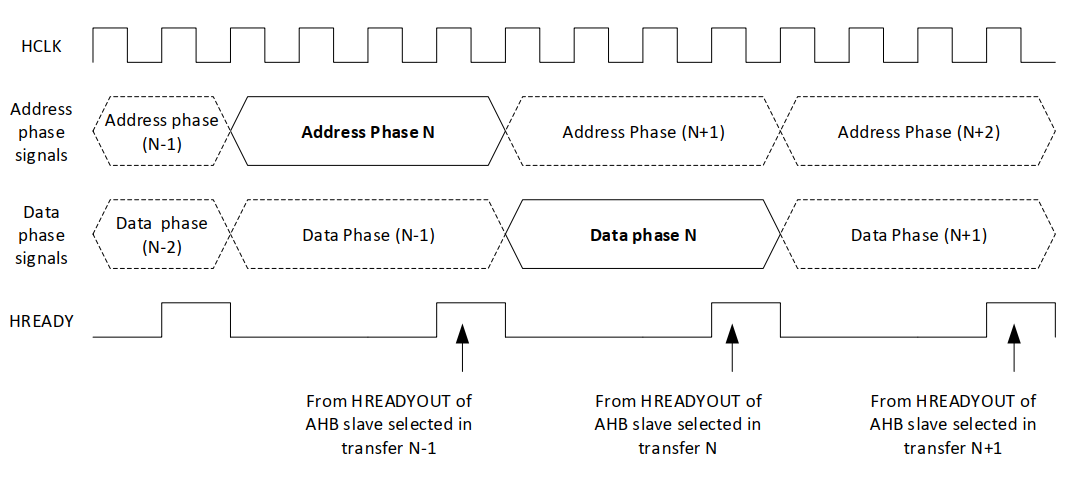

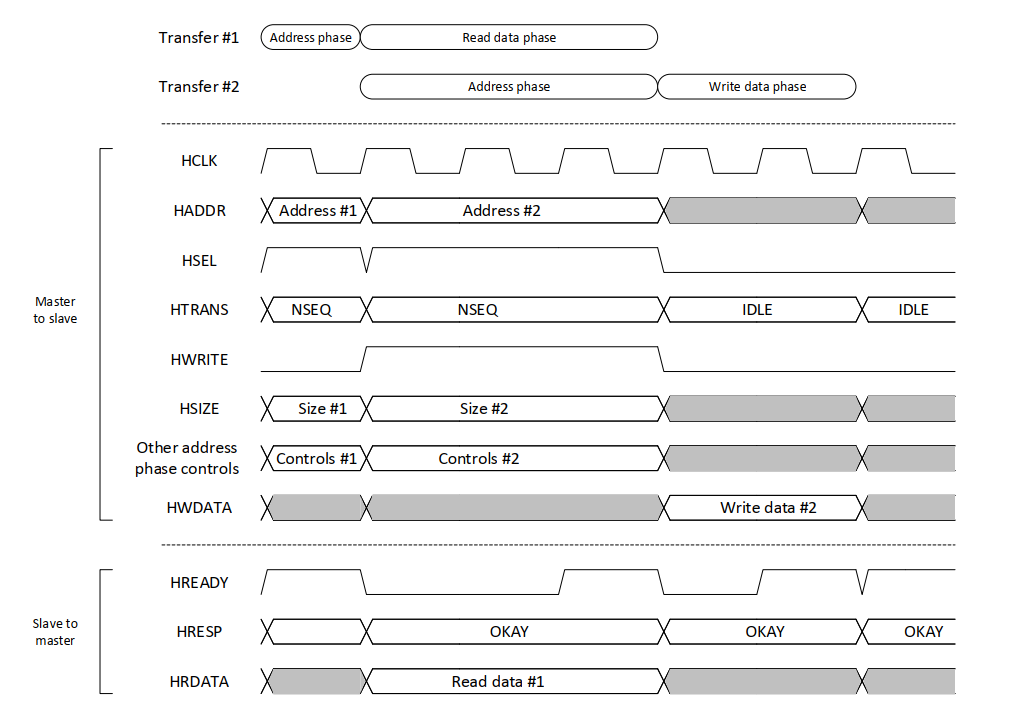

每一次传输都包含一个地址阶段和一个数据阶段,传输可被流水化,也就是说,本次传输中的地址阶段和上次传输中的数据阶段共同进行,具体行为如下图所示:

当前激活的AHB从设备在数据阶段会令HREADYOUT信号有效,该信号会被从设备信号多路选择器传输到主设备的HREADY端口。

如果一个AHB从设备当前未被选中,则该设备的HREADYOUT信号应为高以表示该设备已准备好。

一个最小的AHB系统包含如下三个组件:

- 地址译码器:基于HADDR输入信号,生成HSEL信号用于从设备的选择以及AHB从设备信号多路选择器。

- AHB从设备选择器:将多个从设备连接到一个单独的AHB段(Segment)。

- 默认从设备:这是一个特殊的AHB从设备,当HADDR不在任何其它AHB从设备的地址范围内时,该设备才会被选中,通常该设备被选中是由于系统发生了一些错误(例如由于C指针处理器错误,软件尝试读取无效的存储器位置),该从设备在被访问时只会返回一个错误响应,对该设备的写出数据会被忽略,并且对于读请求,该设备会永远返回0。如果地址空间被完整分配给了其它所有的从设备,则默认从设备可以不使用。

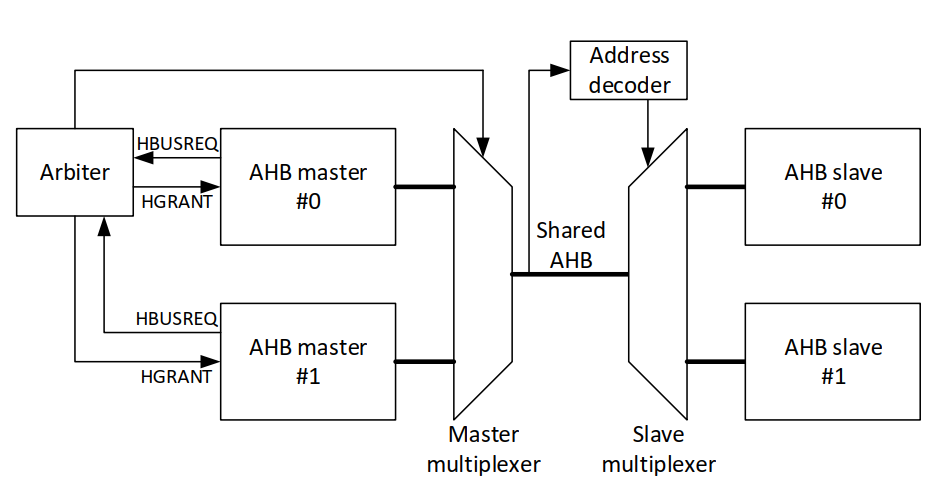

多主设备的互联方式

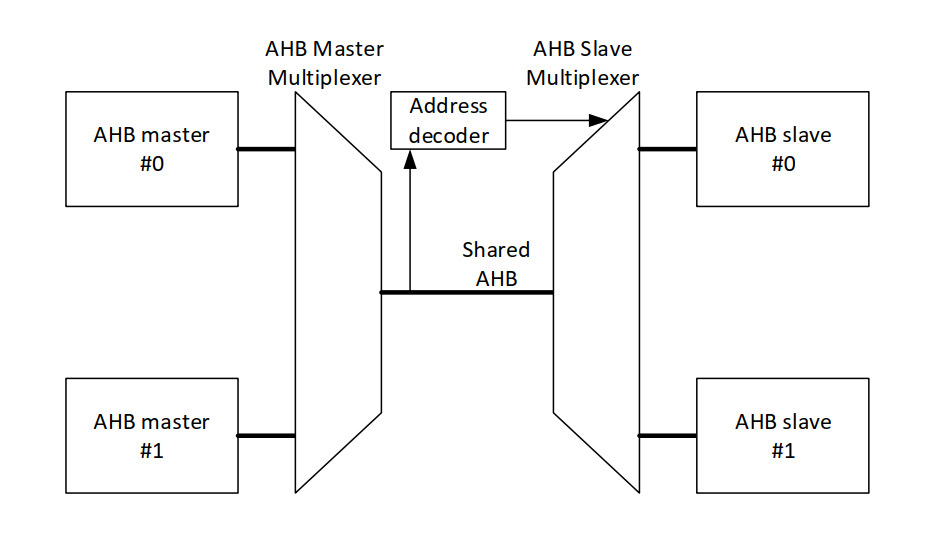

在早期的AMBA 2规范中,多个主设备使用一个主设备信号多路选择器,该选择器由总线仲裁器控制,同时,从设备返回的数据由从设备信号多路选择器选择,并最终传递给总线总设备,其互联方式如下图所示:

仲裁步骤如下:

- 主设备首先使能HBUSREQ信号。

- 仲裁器经过仲裁后,将仲裁结果通过HGRANT信号返回给对应的主设备。

- 获得总线的主设备在总线上开始传输,未获得总线的主设备放弃传输。

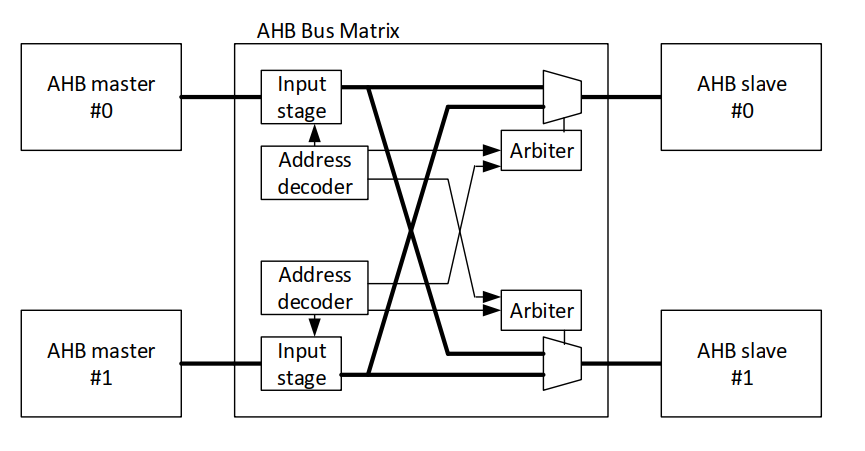

可见,这种方法会极大地限制总线的最大带宽,因此在多层AHB中使用了一种新的支持多主设备的方法,在这种方法中,一个关键性的组件被称为AHB总线矩阵,其互联方式如下所示:

这种方式与早期AMBA 2最大的不同在于,当两个主设备访问不同的两个从设备时,可以同时进行,而不需通过仲裁决出传输顺序。

为了解决多个主设备访问同一个从设备的冲突问题,每一个主端口(连接到AHB从设备的端口)都有一个仲裁器,如果一个主设备请求的从设备正在被另一个主设备使用,传输请求就会被保存在输入阶段的Buffer中,通过这样的方式,舍弃掉了HBUSREQ与HGRANT信号。

当然,如果对总线带宽的要求不高,并因此想要简化总线设计,仍然可以沿用AMBA 2时代的互联方式,只是在其中去掉了AMBA 2时代的仲裁器,而是在AHB主设备信号多路选择器中集成与AHB5中同样的输入阶段及仲裁器,互联方式如下图所示:

0x03 AHB传输时序

下图是一个最简单的时序图,首先发生了一个AHB从设备读操作,然后是一个写操作,最后转为空闲:

上图中,读操作有两个等待周期,写操作有一个等待周期(根据HREADY的信号变化判断)。

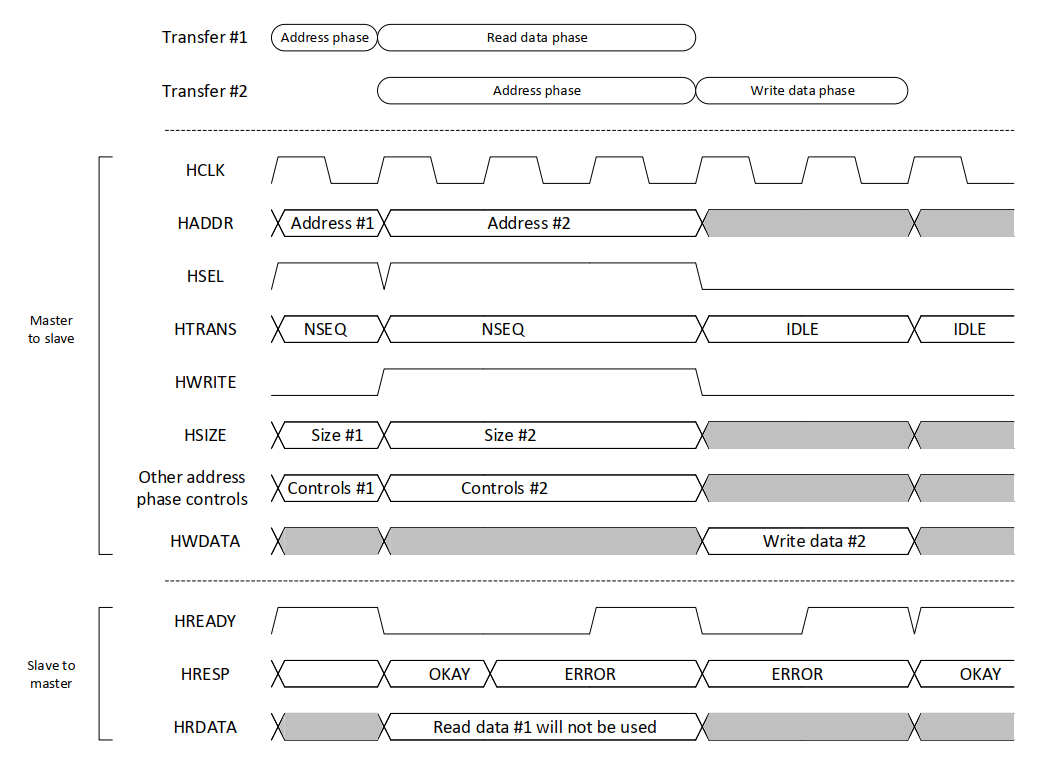

如果读操作和写操作发生错误,时序就会变成下面这样:

0x04 参考文献

System-on-Chip Design with Arm Cortex-M Processors Reference Book